Digitale Schaltungstechnik/ Flipflop/ RS-Flipflop

| Titelseite |

|---|

|

Allgemeines

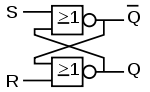

[Bearbeiten]Das RS-Flipflop ist das einfachste Flipflop.

Liegt am S-Eingang (Set) ein 1-Signal, und am R-Eingang ein 0-Signal dann springt der Ausgang auf 1. Dieser Zustand hält so lange an, bis am R-Eingang (Reset) ein 1-Signal liegt.

Liegt am R-Eingang (Reset) ein 1-Signal, und am S-Eingang ein 0-Signal dann springt der Ausgang auf 0. Dieser Zustand hält so lange an, bis am S-Eingang (Set) ein 1-Signal liegt.

Liegt auf beiden Eingängen ein 1-Signal, hat der Ausgang einen undefinierten Zustand.

Liegt auf beiden Eingängen ein 0-Signal, hat der Ausgang den vorher gespeicherten Zustand

Wahrheitstabellen

[Bearbeiten]Zur Darstellung von Flipflops in Wahrheitstabellen gibt es mehrere Möglichkeiten.

| Als erstes die ausführliche: |

| ||||||||||||||||||||||||||||||||

| Diese zeigt alle Zustände und Übergange. Eigentlich ist es ein Impulsdiagramm in Form einer Tabelle.

Die Kommentare sind dabei optional. | |||||||||||||||||||||||||||||||||

| In der gekürzten Form sieht das gleiche Flipflop wie folgt aus: |

| ||||||||||||||||||||||||||||||||

| meint dabei den Wert, den Q zuvor hatte, also Speichern. | |||||||||||||||||||||||||||||||||

Impulsdiagramm

[Bearbeiten]Ersatzschaltbilder

[Bearbeiten]Zusatzinformationen

[Bearbeiten]Der undefinierte Zustand (1 am R- und am S- Eingang) kann verhindert werden. Dazu muss an einem der Eingänge ein UND-Gatter vorgeschaltet werden, wodurch ein Setz- oder Rücksetzvorrang erreicht werden kann.

-

Setzvorrang

-

Rücksetzvorrang

Spezifische Gleichung

[Bearbeiten]Bei Setz-Dominantem RS-Flipflop:

Bei Rücksetz-Dominantem RS-Flipflop: